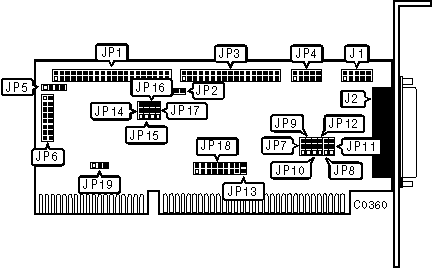

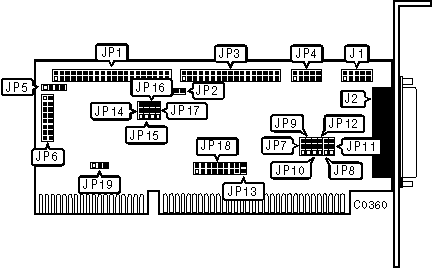

| wie W83787IF | |||

| JP1 | IDE | ||

| JP3 | FDD | ||

| JP4 | ASYN2: COM2/3/4 | ||

| JP5 | Drive Active LED | ||

| JP6 | Game Port | ||

| J1 | ASYN1: COM1/3/4 | ||

| J2 | LPT1/2/3 | ||

| JP2 | open: Two HDD support closed: Single HDD support |

legt IDE Pin 34 (PDIAG) auf GND | |

| JP13 | open: bidirectional LPT close: unidirectional LPT |

legt IC Pin 18 (PRTOE) auf GND | x |

| JP14 | 1-2: Floppy disabled (pulled up) 2-3: Floppy enabled (open/pulled down) |

IC Pin 2 (FDCEN) | x |

| JP15 | 1-2: IDE address is 1F0-1F7 (3F6-3F7) (open/pulled up) 2-3: IDE address is 170-177 (376-377) (pulled down) |

IC Pin 95 (HADSEL) | x |

| JP16 | 1-2: IDE disabled (pulled up) 2-3: IDE enabled (open/pulled down) |

IC Pin 94 (IDEEN) | x |

| JP17 | 1-2: Floppy address is 3F0-3F7 (pulled up) 2-3: Floppy address is 370-377 (pulled down) |

IC Pin 92 | |

| JP19 | 1-2: Game port disabled (2 pulled up) 2-3: Game port enabled () [1 ist pulled up] [2 geht an die 4 Gates des 74LS125] [3 geht an Pin 41] |

IC Pin 41 an 3 | |

| JP18 [123] |

1: ASYN1 IRQ4 2: ASYN1 IRQ3 3: ASYN1 IRQ5 |

IC Pin 37 (IRQ4) | x |

| JP18 [456] |

4: ASYN2 IRQ3 5: ASYN2 IRQ4 6: ASYN2 IRQ5 |

IC Pin 44 (IRQ3) | x |

| JP18 [78] |

7: PRN IRQ7 8: PRN IRQ5 |

IC Pin 23 (IRQ7) | x |

| JP7/JP8 | JP7 1-2 (H), JP8 1-2 (H): ASYN1 disabled JP7 2-3 (L), JP8 1-2 (H): ASYN1 COM1 (3F8) JP7 1-2 (H), JP8 2-3 (L): ASYN1 COM3 (3E8) JP7 2-3 (L), JP8 2-3 (L): ASYN1 COM4 (2E8) |

JP7 an IC Pin 46 (HURAS0) JP8 an IC Pin 38 (HURAS1) |

x |

| JP9/JP10 | JP9 1-2 (H), JP10 1-2 (H): ASYN2 disabled JP9 2-3 (L), JP10 1-2 (H): ASYN2 COM2 (2F8) JP9 1-2 (H), JP10 2-3 (L): ASYN2 COM4 (2E8) JP9 2-3 (L), JP10 2-3 (L): ASYN2 COM3 (3E8) |

JP9 an IC Pin 45 (HURBS0) JP10 an IC Pin 43 (HURBS1) |

x |

| JP11/JP12 | JP11 1-2 (H), JP12 1-2 (H): PRN disabled JP11 2-3 (L), JP12 1-2 (H): LPT1 (378) JP11 1-2 (H), JP12 2-3 (L): LPT2 (278) JP11 2-3 (L), JP12 2-3 (L): LPT3 (3BC) |

JP11 an IC Pin 35 (HPRTAS0) JP12 an IC Pin 36 (HPRTAS1) |

x |

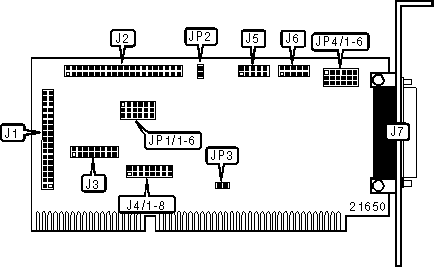

| wie W83787IF | |||

| J1 | Floppy | ||

| J2 | IDE | ||

| J3 | Game Port | ||

| J5 | ASYN2: COM2/3/4 | ||

| J6 | ASYN1: COM1/3/4 | ||

| J7 | LPT1/2/3 | ||

| JP2 | Drive Active LED | ||

| JP1[1] | 1-2: IDE address is 1F0-1F7 (3F6-3F7)* (open/pulled up) 2-3: IDE address is 170-177 (376-377) (pulled down) |

IC Pin 95 (HADSEL) | x |

| ?JP1[2] | 1-2: Floppy address is 3F0-3F7 (pulled up) 2-3: Floppy address is 370-377 (pulled down) |

IC Pin 91 (GIOSEL) | |

| ?JP1[3] | 1-2: Floppy A/B Swap (pulled up) 2-3: Floppy normal* (pulled down) |

IC Pin 92 | |

| JP1[4] | 1-2: IDE disabled (pulled up) 2-3: IDE enabled (open/pulled down) |

IC Pin 94 (IDEEN) | x |

| JP1[5] | 1-2: Floppy disabled (pulled up) 2-3: Floppy enabled (open/pulled down) |

IC Pin 2 (FDCEN) | x |

| JP1[6] | 1-2: PC/XT 2-3: PC/AT |

||

| JP2 | 1-9: ASYN1 IRQ4 2-10: ASYN1 IRQ3 3-11: ASYN1 IRQ5 |

IC Pin 37 (IRQ4) | x |

| JP2 | 4-12: ASYN2 IRQ3 5-13: ASYN2 IRQ4 6-14: ASYN2 IRQ5 |

IC Pin 44 (IRQ3) | x |

| JP2 | 7-15: PRN IRQ7 8-16: PRN IRQ5 |

IC Pin 23 (IRQ7) | x |

| JP3 | open: bidirectional LPT close: unidirectional LPT |

legt IC Pin 18 (PRTOE) auf GND | x |

| JP4[12] | 1: 1-2 (H), 2: 1-2 (H): ASYN1 disabled 1: 2-3 (L), 2: 1-2 (H): ASYN1 COM1 (3F8) 1: 1-2 (H), 2: 2-3 (L): ASYN1 COM3 (3E8) 1: 2-3 (L), 2: 2-3 (L): ASYN1 COM4 (2E8) |

1 an IC Pin 46 (HURAS0) 2 an IC Pin 38 (HURAS1) |

x |

| JP4[34] | 3: 1-2 (H), 4: 1-2 (H): ASYN2 disabled 3: 2-3 (L), 4: 1-2 (H): ASYN2 COM2 (2F8) 3: 1-2 (H), 4: 2-3 (L): ASYN2 COM4 (2E8) 3: 2-3 (L), 4: 2-3 (L): ASYN2 COM3 (3E8) |

3 an IC Pin 45 (HURBS0) 4 an IC Pin 43 (HURBS1) |

x |

| JP4[56] | 5: 1-2 (H), 6: 1-2 (H): PRN disabled 5: 1-2 (H), 6: 2-3 (L): LPT1 (378) 5: 2-3 (L), 6: 1-2 (H): LPT2 (278) 5: 2-3 (L), 6: 2-3 (L): LPT3 (3BC) |

5 an IC Pin 36 (HPRTAS1) 6 an IC Pin 35 (HPRTAS0) |

x |

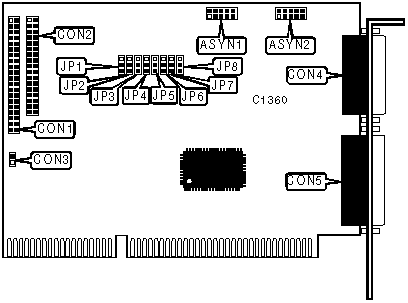

| Jumperstellungen aus Anleitung | ||

| JP1 | LED | |

| JP2 | 1-2: ASYN2=COM* (pulled up) 2-3: ASYN2=IrDA (pulled down) |

IC Pin 92 (URIRSEL) |

| JP3 | 1-2: Floppy A/B Swap (pulled up) 2-3: Floppy normal* (pulled down) |

IC Pin 91 (GIOSEL) |

| JP4 | 1-2: Floppy disabled (pulled up) 2-3: Floppy enabled* (open/pulled down) |

IC Pin 2 (FDCEN) |

| JP5 | 1-2: IDE is primary (1F0)* (open/pulled up) 2-3: IDE is secondary (170) (pulled down) |

IC Pin 95 (HADSEL) |

| JP6 | 1-2: IDE disabled (pulled up) 2-3: IDE enabled* (open/pulled down) |

IC Pin 94 (IDEEN) |

| JP15 | 1-2: Game port enabled* (2 pulled up) 2-3: Game port disabled (2 an Pin 41) [1 geht an die 4 Gates des 74HC126 und ist pulled up] [2 geht an Pin 41] |

IC Pin 41 |

| JP17 | 1-2: IDE IRQ15 2-3: IDE IRQ14* |

|

| großer Block |

IRQs für ASYN1(4*), ASYN2(3*) und PRN(7*) | ASYN1: IC Pin 37 ASYN2: IC Pin 44 PRN: IC Pin 23 |

| JP9/JP10 | JP9 1-2 (H), JP10 1-2 (H): ASYN1 disabled JP9 2-3 (L), JP10 1-2 (H): ASYN1 COM1 (3F8)* JP9 1-2 (H), JP10 2-3 (L): ASYN1 COM3 (3E8) JP9 2-3 (L), JP10 2-3 (L): ASYN1 COM4 (2E8) |

JP9 an IC Pin 46 (HURAS0) JP10 an IC Pin 38 (HURAS1) |

| JP7/JP8 | JP7 1-2 (H), JP8 1-2 (H): ASYN2 disabled JP7 2-3 (L), JP8 1-2 (H): ASYN2 COM2 (2F8)* JP7 1-2 (H), JP8 2-3 (L): ASYN2 COM4 (2E8) JP7 2-3 (L), JP8 2-3 (L): ASYN2 COM3 (3E8) |

JP7 an IC Pin 45 (HURBS0) JP8 an IC Pin 43 (HURBS1) |

| JP11/JP12 | JP11 1-2 (H), JP12 1-2 (H): PRN disabled JP11 1-2 (H), JP12 2-3 (L): LPT1 (378)* JP11 2-3 (L), JP12 1-2 (H): LPT2 (278) JP11 2-3 (L), JP12 2-3 (L): LPT3 (3BC) |

JP11 an IC Pin 36 (HPRTAS1) JP12 an IC Pin 35 (HPRTAS0) |

| JP13/JP14 | JP13 1-2 (H), JP14 2-3 (L): EPP/ECP* JP13 2-3 (L), JP14 1-2 (H): EPP JP13 2-3 (L), JP14 2-3 (L): SPP JP13 1-2 (H), JP14 1-2 (H): Reserved |

JP13 an IC Pin 39 (HPRTM0) JP14 an IC Pin 4 (HPRTM1) |

| ECP DMA [123456] |

1,2: CH0 3,4: CH1 5,6: Ch3 |

1,3,5 an IC Pin 4 (PDRQX) 2,4,6 an IC Pin 18 (PDACKX) |

| ungeprüfte Jumperstellungen | |

| CON1 | IDE |

| CON2 | FDD |

| CON3 | Drive Active LED |

| CON4 | Game Port |

| CON5 | LPT1/2/3 |

| ASYN1 | COM1/2 |

| ASYN2 | COM2/1 |

| 1-2 entspricht RP1-Seite (Pullup-Widerstände) | |

| J1 | 1-2: Game port enabled 2-3: Game port disabled |

| J2 | 1-2: factory configured |

| J3 | 1-2: Floppy enabled (pulled up) 2-3: Floppy disabled (pulled down) |

| J3,J4,J5 | J3 1-2, J4 1-2, J5 1-2: ASYN1=COM1, ASYN2=COM2 J3 1-2, J4 2-3, J5 1-2: ASYN1=COM1, ASYN2=disabled J3 2-3, J4 1-2, J5 1-2: ASYN1=COM2, ASYN2=COM1 J3 2-3, J4 2-3, J5 1-2: ASYN1=COM2, ASYN2=disabled J3 2-3, J4 1-2, J5 2-3: ASYN1=disabled, ASYN2=COM1 J3 1-2, J4 1-2, J5 2-3: ASYN1=disabled, ASYN2=COM2 J3 2-3, J4 2-3, J5 2-3: ASYN1=disabled, ASYN2=disabled |

| J6 | IC Pin 7 |

| J7,J8 | JP7 1-2, JP8 2-3: LPT1 JP7 1-2, JP8 1-2: LPT2 JP7 2-3, JP8 1-2: LPT3 JP7 2-3, JP8 2-3: PRN disabled |